Goals of Synthesis

- Timing Optimization: One of the most important goals of synthesis is to ensure that the design meets all timing constraints, such as clock frequency, setup time, and hold time, so that the circuit operates correctly at the desired speed.

- Area Optimization: Synthesis aims to reduce the total area of the design by using an optimal number of standard cells, which helps in lowering the overall chip size and manufacturing cost.

- Power Optimization: Another key goal is to minimize power consumption by optimizing switching activity, leakage power, and using efficient logic structures.

- Netlist Generation: The optimized design is converted into a gate-level representation using standard cells from the target technology library. This netlist describes how different logic gates and sequential elements are interconnected through nets to form a complete circuit.

- Ensure Functional Correctness: Synthesis must preserve the original functionality of the RTL design, ensuring that the gate-level netlist matches the original RTL, typically verified through Logical Equivalence Checks (LEC).

Inputs required for Synthesis

- RTL (Register Transfer Level Code)

- SDC

- Timing Library File (.lib)

- Technology File

- MMMC File

- UPF (Unified Power Format)

- RC Coefficient File (TLU+ for Synopsis and QRC for Cadence)

- Physical Library File (.lef)

- Floorplan DEF

Click here for more details on the inputs required in Physical Design.

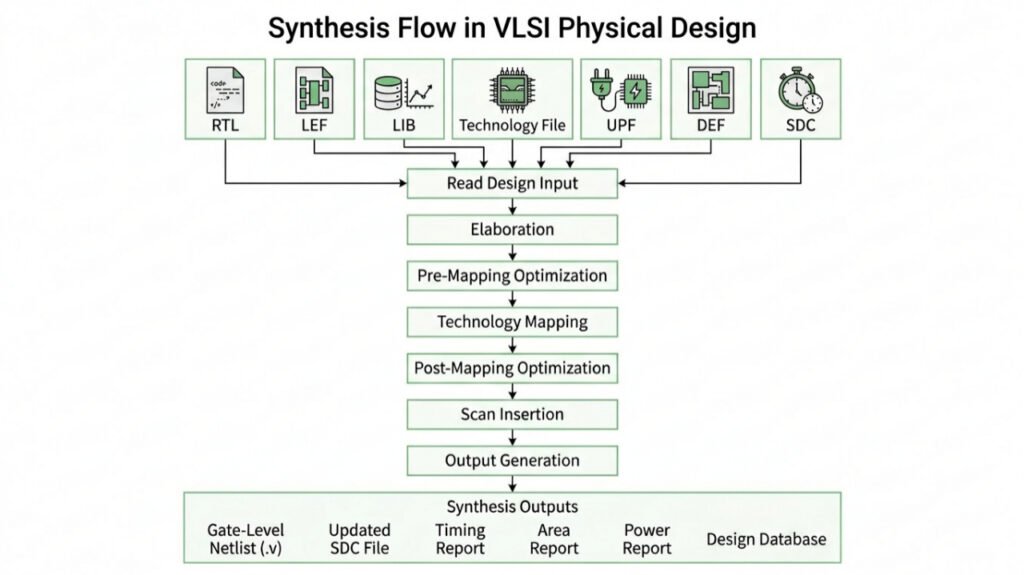

Steps Involved in Synthesis

The following are the key steps involved in the synthesis process:

- Elaboration: In the elaboration stage, the synthesis tool reads the RTL code and builds a hierarchical representation of the design by resolving all modules and connections. The logic is converted into a technology-independent format, such as generic or GTECH cells. During this process, the tool checks for issues like duplicate definitions, unresolved references, and timing loops. Any such problems must be corrected at the RTL or library level before proceeding further.

- Pre-Mapping Optimization (Logic-Level Optimization): Pre-mapping optimization is the stage in synthesis where the design is improved at a technology-independent level by simplifying and restructuring the logic before it is mapped to actual standard cells. During pre-mapping optimization, the synthesis tool analyzes the logical structure of the design and applies various techniques like Boolean Logic Simplification, Redundant Logic Removal, Logic Restructuring, etc., to reduce complexity, eliminate unnecessary logic, and prepare a more efficient representation for mapping.

- Technology Mapping: Technology mapping is the process of converting technology-independent logic into a specific technology-dependent logic where the tool uses the standard cells from the target library by decomposing logic, selecting appropriate gates, and optimizing the design for timing, area, and power. The result is a gate-level netlist ready for further optimization and physical implementation.

- Post-Mapping Optimization (Gate-Level Optimization): Once the design has been mapped to real standard cells, the synthesis tool performs post-mapping optimization using actual cell characteristics such as delay, power, and drive strength, along with estimated interconnect effects, to further refine the design and ensure it meets timing, area, and power requirements.

- Outputs Generation: The main outputs of synthesis include the gate-level netlist, updated constraint file, timing, area, and power reports, and a design database used for further optimization and Physical Design.

Types of Synthesis

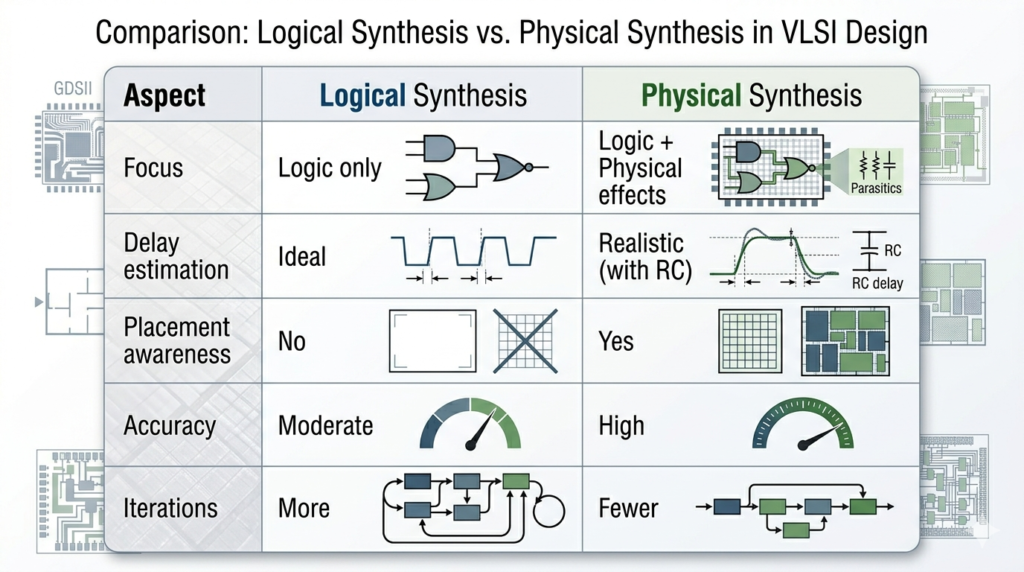

Logical Synthesis: Logical synthesis is the process of converting a high-level Register Transfer Level code (described in Verilog or VHDL) into a gate-level netlist by mapping the design onto standard cells, while optimizing for timing, area, and power based on given constraints.

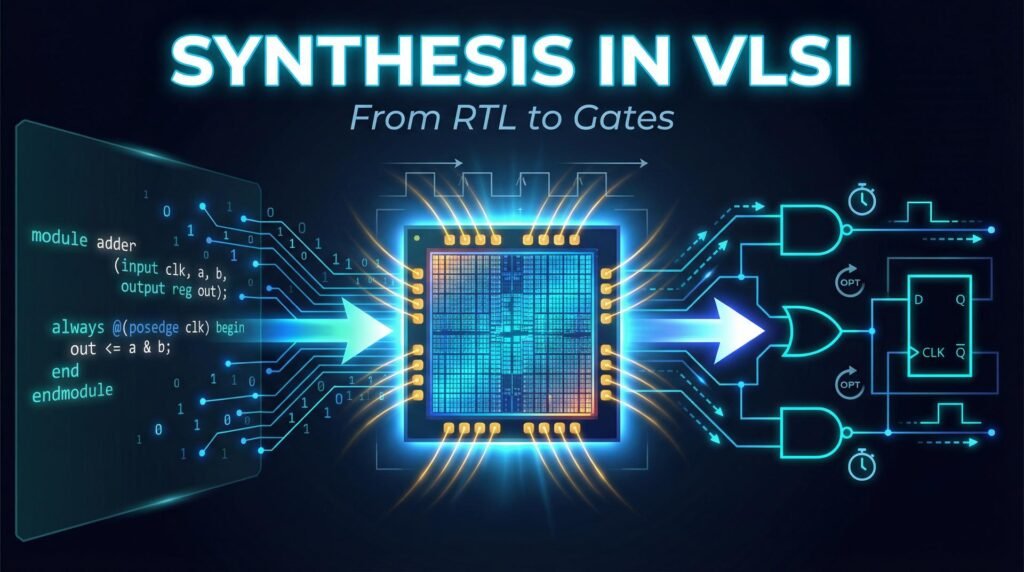

Synthesis is the process of transforming a high-level Register Transfer Level (RTL) code, usually written in a hardware description language like Verilog or VHDL, into a gate-level netlist by mapping the logic onto available standard cells, while optimizing the design to meet timing, area, and power requirements as defined by the given constraints.

RTL code, Timing constraints (SDC) and Target technology libraries (.lib) are the main inputs required for logical synthesis. The synthesis tool analyzes the RTL and transforms it into a network of logic gates using standard cell libraries. During this process, it optimizes timing, area and power.

Limitations of Logical Synthesis

Traditionally, the design flow followed a straightforward approach where RTL was first synthesized into a gate-level netlist, which was then passed to Physical Design for placement and routing. This method worked effectively for older technology nodes where physical effects like wire delay and parasitics were relatively small.

However, as technology advanced, several challenges emerged. Factors such as increased wire delays, voltage drops, parasitic effects, and routing congestion started significantly impacting the design. As a result, the behavior of the logically synthesized design often differed from its final physical implementation. This mismatch led to multiple iterations between synthesis and place-and-route stages, increasing design time and making timing closure more difficult to achieve.

Physical Synthesis: Physical synthesis is an advanced synthesis technique in VLSI design where the optimization of a circuit is performed by considering not only logical functionality but also physical implementation effects such as placement, routing, interconnect delays, and parasitic elements. Unlike traditional synthesis, which assumes ideal conditions, physical synthesis uses early physical information to generate a gate-level netlist that is more accurate, realistic, and better aligned with the final silicon implementation, thereby improving timing, area, and power results.

In traditional flows, synthesis assumed ideal interconnects, but as the technology advances, factors like wire delays, IR drop, parasitic capacitance, and routing congestion significantly affect performance. Because of this mismatch, designs often required multiple iterations between synthesis and place-n-route stages, increasing more run time and making timing closure more challenging.

To overcome these issues, physical synthesis incorporates the effects early in the design process instead of waiting until placement and routing are completed. By doing so, it reduces unexpected timing violations, improves correlation between synthesis and final implementation, and minimizes the number of design iterations required.

Advantages of Physical Aware Synthesis

- Improved Timing Accuracy

- Better Correlation with Physical Design

- Faster Timing Closure

- Reduced Iterations Between Stages

- Optimized Area and Power

- Early Detection of Design Issues

- Improved Design Convergence